圖片來源:3nm_Chip_Production_main5-2.jpg

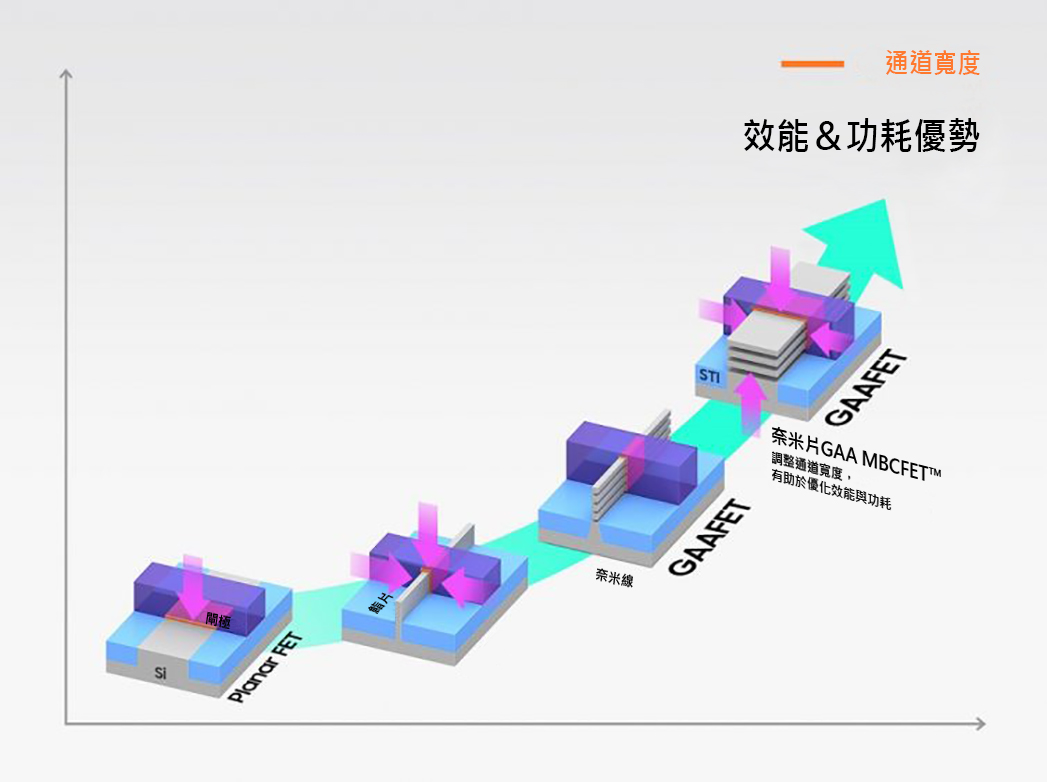

三星號稱量產的3奈米製程,是GAAFET架構的MBCFET,是奈米管(nano wire)架構(第一代GAA)而已,而更先進的奈米片(nano sheet)架構(第二代GAA)還在研發中,紙上規格真的好棒棒,但三星號稱量產的3奈米製程不但要微縮製程,還同時更改了最底層的半導體元件架構,初始的製造良率一定很糟糕的,難怪雖然號稱已經量產,但首發客戶是誰仍在保密中。 (台積電到了2奈米製程才採用GAAFET架構,但直接是第二代的奈米片(nano sheet)架構。因為台積電在奈米片架構上研發超過15年,又有量產22奈米製程奈米片架構SRAM的實際成果,這次台積電說有極大信心在2025年量產2奈米的奈米片架構MBCFET,領先三星與Intel,是可信的預測。)

另外,美國禁止3奈米以下製程的美國EDA軟體出口中國(中國客戶不能使用),當然包含了文中所述的前四大EDA軟體商。這是因為Cadence與Synopsys是美商不用討論,而Siemens購併了Mentor等美商, Ansys是購併了Apache Design等美商,他們的技術來源都是美國,所以美國商務部是一定管得著的。

當然,這個出口限制包括文中所述他們得到三星3奈米(GAAFET)製程認證,也包括與台積電3奈米(FINFET)認證的所有EDA軟體。

還有,因為這些經過特定晶圓代工廠特定製程認證的EDA軟體及智財庫,必定含有晶圓代工廠的製程參數等營業秘密,才能進行驗證與簽核,所以通常是由晶圓代工廠領頭,組成EDA Alliance(晶片電子設計自動化聯盟),讓簽約的客戶取得授權使用這些經過認證且位於雲端的EDA軟體及智財庫(所以不可能被客戶偷偷下載而複製或盜用),才能夠加快晶片設計速度,降低其設計成本,保障EDA廠商及晶圓代工廠的智慧財產權,並保證被簽核的設計方案能夠被該晶片代工廠用所認證的特定製程製造出來(製造良率是另一回事)。

舉例來說,三星所組的EDA Alliance叫做先進製程晶圓代工生態圈(SAFE™),而台積電成立的TSMC EDA Alliance,是 TSMC Open Innovation Platform® (OIP)雲端聯盟中的最重要組成,合作創始成員包括亞馬遜AWS及微軟Azure等雲端服務業者,以及益華電腦(Cadence)及新思科技(Synopsys)等EDA供應商。